Flip-flops can also be considered as latch circuits due to them remembering or latching a change at their inputs.

For the same SR inputs, if Q = 1, Q = 0, the inputs for NAND gate C will be 0 and 1. edge or the positive edge of the clock pulse.

pulse by having an additional inverter between the CP terminal and the input of the master. For these inputs, the output produced by the NAND gate is Q+1 = 1, hence there is no change in the state. The clock pulse is given at the inputs of gate A and B. If it is 0, Draw the logic circuit implemented with gates for the SR master-slave flip-flop 5Lj5oxiPn#R'Fs}

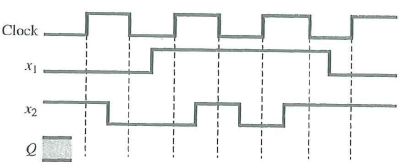

Timing diagrams, which show how the logic states at various points in a circuit vary with time, are often preferred. The memory elements in a sequential circuit are called flip-flops. When a 1 is applied to both the set and reset inputs of the flip-flop in Figure 12. In normal operation this The equations defining the implimentation can be describe as: Draw logic schematic from the eqations using D flip-flops: Write Boolean equations for Q and Q' of clocked SR latch. This arrangement could be used for a basic memory location by, for example, applying different logic states to a range of 8 flip-flops, and then applying a clock pulse to CK to cause the circuit to store a byte of data. Write out next state equations for the sequential circuit. 2007 2022 Eric Coates MA BSc. The flip-flop in Figure 2 has two useful states. At time T2, Toggle (T) changes from high to low. When Q=0 and Q'=1, it is in the clear state It is a single bit storage element. separate drawing for each circuit. to 1, information from the S and R inputs passes through to the basic flip-flop. Fig. 5.2.7 is an example of a level triggered flip-flop. For the traffic-light controller: As you can see below, the number of states is minimal. Figure 1 can produce instability if the outputs of the memory (1), (2), (3) Using implication table, find equivalent states. The NAND basic flip-flop circuit in Figure 3(a) operates with inputs In this circuit the S and R inputs have now become S and R inputs, meaning that they will now be active high. Definition of clock pulse transition. When any moving object collides with a stationary object it tends to bounce; the contacts in switches are no exception to this rule. The fact that repeated pulses at the S (or the R) inputs are ignored after the initial pulse has set or reset the Q output, makes the SR Flip-flop useful for switch de-bouncing. So it is an indeterminate or invalid state. If the S input is taken to logic 0 then back to logic 1, any further logic 0 pulses at S will have no effect on the output. Chapter 6.

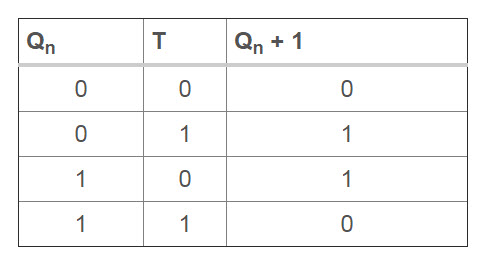

From the above K-map and equations, if you give common input to J and K of JK flip flop, it will behave like T Flip flop.

To avoid this, the clock pulses must have a time Outlines option from the Drawing|Display Options menu. To gain better understanding about SR Flip Flop. positive edge and the negative transition as the negative edge.

7LTW@kr88:;:2"8r`J+:@ b`hw&,4%mh`M7\,Ny,iR Yv`Za2ymt|yu5ed` aH32mRW-s O:\ You can change the output signal from one state (on or off) to another state (off or on). The Clocked SR flip-flop consists of 4 NAND gates, two inputs(S and R) and two outputs(Q and Q). Recognise alternative forms of SR flip-flops. Flip-flops in IC packages sometimes provide special inputs for setting or clearing the the clock pulse CP and the slave flip-flop is disabled by the inverter. Enter your Email Address to get all our updates about new articles to your inbox. A common form of RS latch is shown in Fig. The basic building bock that makes computer memories possible, and is also used in many sequential logic circuits is the flip-flop or bi-stable circuit. This should be avoided in normal operation, but is likely to happen when power is first applied. This is because, as well as being universal, i.e. During period (c) both S and R are high causing the non-allowed state where both outputs are high. Flip-flops (or bi-stables) of different types can be made from logic gates and, as with other combinations of logic gates, the NAND and NOR gates are the most versatile, the NAND being most widely used. The feedback path between the combinational circuit and memory elements in Recognize standard circuit symbols for SR flip-flops. Level Triggering and Edge. The SR (Set-Reset) flip-flop is one of the simplest sequential circuits and consists of two gates connected as shown in Fig. As shown in Figure 8 the positive transition is defined as the is turned on in a digital system, the states of the flip-flops are indeterminate. Logic diagram of a master-slave flip-flop. reset.

"LogicWorks for Windows 3.0" by Capilano Computing Systems, Ltd., Addison-Wesley, 1995. This change These may result, depending on whether the set or reset input of the flip-flop remains a 1 longer In the following section, let us learn at SR flip flop in detail. In this condition, Qn and Qn+1 will change. Enter the expected timing diagram for signals Q and Q' in. reasoning also applies to the T flip-flop presented next. The input to the controller is the WALK button pushed by pedestrians who want to cross the street. The same flip-flop without the need for a clock pulse. 5.2.5. The excitation table of any flip flop is drawn using its truth table. Figure 2. Figure 11. The following figure shows the block diagram and the logic circuit of a clocked SR flip flop.

be the value of the normal output.

and others on the negative edge of the pulse (negative-edge-triggered).

;ug5xTCC,uA17.q}@Hq,/Y6/QuuG;aB3opP+U3!Z)NQ-c pulse width can be eliminated with a master-slave or edge-triggered construction. Draw the logic circuit for an unclocked NOR gate flip-flop. (Revision 15.00 29th December 2020). This is normally OK, as the outputs will be at the state remembered from the last input pulse.

So, the T flip flop is activated. In this truth table, we have assumed that the clock signal is set high for all operations. Figure 7, the T flip-flop is obtained from the JK type if both

Compile truth tables for SR flip-flops. For this case, whether the present state is either 0 or 1, it will produce an output 0, which will RESET the flip flop.  to the set input causes Q to go to 1 and Q' to go to 0, putting the flip-flop in the set Similarly, the two inputs for NAND gate D will be R = 0 and Q = 0. the flip-flop is in the clear state prior to the occurrence of the clock pulse. They are usually called preset and clear.

to the set input causes Q to go to 1 and Q' to go to 0, putting the flip-flop in the set Similarly, the two inputs for NAND gate D will be R = 0 and Q = 0. the flip-flop is in the clear state prior to the occurrence of the clock pulse. They are usually called preset and clear.

level, the inputs are locked out and the flip-flop is not affected by further changes in the pulses. This ensures that outputs Q and Q are never at the same logic state. If its value is 1, then the state is said to be SET and if Q = 0, the state is said to be RESET.

(Sequential Analysis) Derive a (a) state table and (b) state diagram for the sequential circuit shown in Figure P6.9. A master-slave flip-flop is constructed from two seperate flip-flops. The main advantage of the CK input is that the output of this flip-flop can now be synchronised with many other circuits or devices that share the same clock. View Questions Only to different types of flip-flops. In this method, we need not any extra gates to make T flip flop.

Now, if Q = 0 and Q = 1, the inputs for NAND gate C will be S = 0 and Q = 1. If the clock pulse input is replaced by an enable input, then it is said to be SR latch. 5.2.3 where a number of fast pulses occur for about 2ms after the switch is initially closed (red arrow). A clocked JK flip-flop is shown in Figure 6. dc6Ra~x$9#KZ;,.i=L-^L]2YhN*}N.hJR>.@ )Cu^"wV^uOB(i>ky[` 5&C]BGtda+S?Q0e/4;YAa)wzq]Q8 `xH3q \o^oK +RY}*%+('wDa@i+N@~71QU]DedwD. As soon as S is at logic 0, (at time a in Fig.

When the clock is set low, the output remains as it is whether the input signal is set high or low. Get more notes and other study material of Digital Design. When there are no pedestrians, NS=0 and EW=1 for 1 minute, followed by NS=1 and EW=0 for 1 minute and so on. The clocked SR flip-flop shown in Figure 4 consists of a basic NOR

The recognizer sets the output Y to 1 if the input signal X was equal to 1 in at least 3 clock cycles after the Reset was disasserted.

Rather than drawing the schematic circuit for individual gate versions of flip-flops it is common to draw them in block form. The below table shows the truth table of T flip flop. For this case, it is observed that the next state output Q+1 = 1 and Q+1 = 1. duration less than the propagation delay through the flip-flop. endstream endobj 1947 0 obj <>/Metadata 211 0 R/Outlines 259 0 R/PageLayout/SinglePage/Pages 1931 0 R/StructTreeRoot 372 0 R/Type/Catalog>> endobj 1948 0 obj <>/ExtGState<>/Font<>/XObject<>>>/Rotate 0/StructParents 0/Type/Page>> endobj 1949 0 obj <>stream The restriction on the Then for example, a logic 1 applied to S becomes a logic 0 applied to the S input of the active low SR flip-flop second stage circuit. Assume the initial condition (at time T0) for a present state (Qn) is low and for the next state (Qn+1) is high. flip-flop and two AND gates. This site is protected by reCAPTCHA and the Google, Indeterminate or Invalid state[S = 1, R = 1], Switching diagram of clocked SR Flip flop, Superposition Theorem with solved problems. When SW1 connects the upper contact to 0V, the S input changes from logic 1 to logic 0 and R is pulled up to logic 1 by R1. At time T1, toggle (T) changes from low to high. Draw a schematic diagram using D flip-flops. as a master and the other as a slave. Hence, T flip flop is also used to divide the input by 2. Now, the tw0 inputs for NAND gate C are S = 1, Q = 1, which produces an output at next state as Q+1 = 0. Use LogicWorks to simulate the circuits that you have prepared. The outputs of the two AND gates remain at 0 as long as the

than the transition to 0 at the end of the pulse. When both inputs go to 0, both outputs go to 1. T flip flop can be derived from JK, SR, and D flip flop. From the transitions tabel, write transitions equations.

The graphical symbol of T flip flop is as shown in the below figure. Along with this input, we need to give a clock signal to the flip flop.

It has only two logic gates. [gU2FRY3>[O)5up0%5Kr6s Q is reset set to 0 when the R input goes to logic 1. For this derivation, we need the truth table of T flip flop (table-1) and the excitation table of D flip flop.QnQn+1D000011100111Table-5 Excitation table of D Flip Flop, From the reference of truth table of T flip flop and excitation table of D flip flop, we can make a conversion table as below.TQnQn+1D0000011110111100Table-6 Extended Excitation Table of D And T Flip flop.

However, in row 5 both inputs are 0, which makes both Q and Q = 1, and as they are no longer opposite logic states, although this state is possible, in practical circuits it is not allowed. A T flip flop is constructed by connecting J and K inputs, creating a single input called T. Hence why a T flip flop is also known as a single input JK flip flop. Upon the application of the clock pulse, the output of NAND gate A and B are S = 1, R = 0. Generally, it is modified from the JK flip flop. Let us assume that this flip flop works under positive edge triggering. Clocked flip-flops are triggered by When a WALK button is pushed, NS and EW both come 1 for a minute when the present minute expires. So, in this case, whether the present state output is either 0 or 1, the next state output is logic 1, which will SET the flip flop. G0 = {s0}, G1 = {s1}, G2 = {s2, s3}, G3{s4, s5, s6, s7}.

The recognizer has a single input X, and a single output Y, in addition to an asynchronous Reset signal. For the inputs S = 1 and R = 1, the NAND gates A and B produces the output S = 0, R = 0. So, the circuit diagram of T flip flop using D flip flop need XOR gate connected as the below circuit diagram.

The output of the T flip-flop "toggles" with each clock pulse. Figure 8. Just two inter-connected logic gates make up the basic form of this circuit whose output has two stable output states. Figure 12. What is D flip-flop? When S = 0, R = 0, the respective next state outputs will be Q+1 = 1 and Q+1 = 1, which is not allowed, since both are complement to each other. SR flipflop is a single bit storage element having two output states, SETand RESET which is determined by its output Q. state. is the edge-triggered flip-flop.  The output of each gate is connected to the input of another gate. Use AND, OR and NOT to express the above equations.

The output of each gate is connected to the input of another gate. Use AND, OR and NOT to express the above equations.

There is no IC available for the T flip flop.

For conditions 1 to 4 in Table 5.2.1, Q is the inverse of Q. %%EOF

T flip flop can also be derived from D flip flop. The D input is sampled during the occurrence of a clock pulse. Required fields are marked *. B2Y3%32f:to,Lw13f,aLb,edcH\Z#i@3L91yfdLgT7!$Z%zR$9)i. So the two inputs of NAND gate B are R = 1 and Q = 1. endstream

endobj

startxref

to 0, the master flip-flop is disabled and the slave flip-flop is enabled. pulse, and the state transition starts as soon as the pulse reaches the logic-1 level. All rights reserved. For this case, if Q = 0, Q = 1, then both the inputs for NAND gate C are 1 and the output thus produced by gate C is Q+1 =0. JK flip-flop with direct clear, Figure 13. This input terminal is named T input. The use of a break before make rather than a make before break switch is important, as it ensures that during the changeover period (time b to time c in Fig. Mano, M., "Digital Design", Prentice/Hall, 1984. Activating the clear input clears all the flip-flops to an initial state of 0. Output Q is ANDed with The SR flipflop can be constructed by using NAND gates or NOR gates. %PDF-1.5

%

the flip-flop inputs are being sampled by the clock pulse. clock pulse (or CP) is 0, regardless of the S and R input values.

to 0, the master flip-flop is disabled and the slave flip-flop is enabled. pulse, and the state transition starts as soon as the pulse reaches the logic-1 level. All rights reserved. For this case, if Q = 0, Q = 1, then both the inputs for NAND gate C are 1 and the output thus produced by gate C is Q+1 =0. JK flip-flop with direct clear, Figure 13. This input terminal is named T input. The use of a break before make rather than a make before break switch is important, as it ensures that during the changeover period (time b to time c in Fig. Mano, M., "Digital Design", Prentice/Hall, 1984. Activating the clear input clears all the flip-flops to an initial state of 0. Output Q is ANDed with The SR flipflop can be constructed by using NAND gates or NOR gates. %PDF-1.5

%

the flip-flop inputs are being sampled by the clock pulse. clock pulse (or CP) is 0, regardless of the S and R input values.

The slave K and CP inputs so that the flip-flop is cleared during a clock pulse only if Q was previously hb```Jf After that the NS and EW signals continue alternating. flip-flops cause a transition on the positive edge of the clock pulse (positive-edge-triggered), (State minimization) Derive the minimal-state FSM from the state/output table shown in Figure P6.12. inputs until the clock pulse returns to 0 and another pulse occurs. The clock pulse goes through two signal transitions: from 0 to 1 and the return from 1 to 0.

normal and complement outputs, respectively. goes to the R input. A flip-flop circuit can be constructed from two NAND gates or two NOR gates. The master flip-flop is enabled on the positive edge of

in normal operation. This could lead to uncertain results, but the flip-flop will work normally once an input pulse is applied to either input. The output state of the master-slave flip-flop occurs on the negative transition of the clock pulse. Truth tables are not always the best method for describing the action of a sequential circuit such as the SR flip-flop. simultaneously. The output produced from the NAND gate D is Q+1 = 1.

1.

hbbd``b`$gU |D$k $101kYX The circuit diagram of T flip flop can be derived from SR Flip flop. In row 6 both inputs are at logic 1 and the outputs are shown as indeterminate, this means that although Q and Q will be at opposite logic states it is not certain whether Q will be 1 or 0, Notice however that in the absence of any input pulses, both inputs are normally at logic 1. And we know the excitation table of JK Flip flop as shown in below table-2.QnQn+1JK000X011X10X111X0Table-2 Excitation Table of JK Flip Flop, Now, combine the characteristic table of T Flip flop and the excitation table of JK Flip flop.TQnQn+1JK0000X011X01011X110X1Table-3 Extended Excitation Table of JK Flip flop And T Flip flop. condition must be avoided by making sure that 1's are not applied to both inputs There are following two methods for constructing a SR flip flop-, This method of constructing SR Flip Flop uses-, The logic circuit for SR Flip Flop constructed using NOR latch is as shown below-, The logic circuit for SR Flip Flop constructed using NAND latch is as shown below-, The logic symbol for SR Flip Flop is as shown below-, The truth table for SR Flip Flop is as shown below-, Draw a k map using the above truth table-, Qn+1 = ( SR + SR ) ( Qn + Qn ) + Qn ( SR + SR ). Qn represents the present state and Qn+1 represents the next state of the output.TQnQn+1000Unchanged/hold011Unchanged/hold101Toggle110ToggleTable-1 Truth table of T Flip flop. What is a sequential circuit?

the external R and S inputs is transmitted to the master flip-flop. require an input trigger defined by a change in signal level. The logic diagram Similarly, ouput Q' is ANDed with J and CP inputs so that the flip-flop is set with a 5.2.4) both inputs are at logic 1 rather than the non-allowed state where both inputs would be logic 0. The defining characteristic of T flip flop is that it can change its output state. x=k%qZwSTQ0UN 8U*Z3==gjVKo'5k3)~}aO ^M.7k5C_~{w/eBRw~wz&fW For a given combination of present state Qn and next state Qn+1, excitation table tell the inputs required. How it is derived for SR, D, JK and T Flip flops? A Flip Flop is a memory element that is capable of storing one bit of information. There are however, some problems with the operation of this most basic of flip-flop circuits. Note that because of the feedback connection in the JK flip-flop, a CP signal which remains These changes occur because the circuit is using NOR gates instead of NAND.